Why Quantum Computers Need 1,000 Qubits for One

TL;DR: Cache coherence protocols like MESI and MOESI coordinate billions of operations per second to ensure data consistency across multi-core processors. Understanding these invisible hardware mechanisms helps developers write faster parallel code and avoid performance pitfalls.

Every second, your processor performs billions of tiny negotiations you never see. While you're typing an email or streaming a video, hardware protocols are constantly mediating between your CPU cores, deciding who gets which piece of data, who needs to wait, and who has the freshest copy. Without these invisible referees, your multi-core chip would descend into computational anarchy in milliseconds.

This is the world of cache coherence protocols, and they're the unsung heroes that make modern parallel computing possible. The problem they solve is deceptively simple: when multiple processor cores each have their own cache and they're all working on shared data, how do you make sure everyone sees the same reality? Get it wrong, and cores read stale data, calculations go haywire, and your carefully written multi-threaded code produces garbage.

The two dominant protocols - MESI and MOESI - accomplish this coordination through elegant state machines implemented entirely in hardware. They work so efficiently that most software developers never need to think about them. But understanding how they work unlocks new insights into performance bottlenecks, explains mysterious slowdowns in threaded applications, and reveals the engineering ingenuity required to make billions of transistors cooperate at nanosecond timescales.

In the single-core era of computing, cache coherence was trivial. One processor, one cache, no problem. But when chip designers started cramming multiple cores onto a single die in the early 2000s, they created a consistency nightmare.

Here's why: each core has its own private cache - usually multiple levels, from tiny L1 caches measured in kilobytes to larger L2 and L3 caches measured in megabytes. These caches exist because accessing main memory is glacially slow compared to on-chip cache, often 100 times slower or more. But when multiple cores cache copies of the same memory location, you get a fundamental problem: if Core 1 modifies its cached copy, how do the other cores know their copies are now stale?

Without coordination, you get data races, torn reads, and violations of memory ordering guarantees that programmers depend on. Imagine Core 0 writes the value 42 to variable X, then Core 1 reads X and still sees the old value of 0 because its cache hasn't been updated. Your lock-free algorithm just broke. Your database transaction just lost consistency. Your physics simulation just calculated that objects can pass through walls.

The solution requires hardware-enforced rules about who can read what, who can write what, and what happens when multiple cores want conflicting access. Enter MESI and MOESI, the state machine protocols that have governed cache behavior for decades.

MESI, developed by Mark Papamarcos and Janak Patel at the University of Illinois in 1984, introduced a four-state model that elegantly handles cache coherence. The acronym stands for Modified, Exclusive, Shared, and Invalid - the four states any cache line can occupy.

Modified (M): The cache line is present only in this cache and has been modified. The data is "dirty" - it differs from main memory. This core has exclusive write permission, and before anyone else can access this data, it must be written back to memory or transferred directly to the requesting cache.

Exclusive (E): The cache line is present only in this cache and matches main memory. It's "clean," meaning it hasn't been modified since loading. This state enables a crucial optimization: if a core wants to write to an Exclusive line, it can transition directly to Modified without broadcasting an invalidation message, because no other cache holds a copy.

Shared (S): The cache line may exist in multiple caches and matches main memory. All copies are read-only. If any core wants to write, it must first broadcast an invalidation message to force all other copies into the Invalid state.

Invalid (I): The cache line is stale or absent. Any attempt to read or write this line requires fetching fresh data from another cache or main memory.

Cache coherence protocols operate at cache-line granularity - typically 64 bytes on x86. This means even a single byte modification triggers coherence traffic for the entire 64-byte line, a detail that profoundly impacts performance.

These states form a state machine with precisely defined transitions. When Core 0 reads a memory location, the cache controller broadcasts a read request on the interconnect. Other caches snoop this request - they listen to bus traffic to monitor what other caches are doing. If another cache holds the line in Modified state, it must either provide the data directly or write it back to memory first. If multiple caches hold the line, they all transition to Shared state.

The genius of MESI lies in what it prevents. The Exclusive state eliminates wasteful bus transactions when a processor reads a line that no other core holds. Without the E state, the protocol would need an extra message to upgrade from Shared to Modified, even when no sharing actually exists. This single optimization saves billions of unnecessary bus transactions in typical workloads.

MESI is an invalidation-based protocol, meaning that when one core writes to a Shared line, it invalidates all other copies rather than updating them. This choice reflects a fundamental tradeoff: invalidation requires less bandwidth than update (one message instead of broadcasting the new value), but it means that other cores will incur a cache miss on their next access.

MOESI extends MESI with a fifth state: Owned. This seemingly small addition delivers significant performance benefits in workloads where multiple cores frequently read data that one core has modified.

Owned (O): The cache line holds the most recent, correct copy of the data, which may differ from main memory (like Modified), but other caches may also hold shared copies of this data (like Shared). The cache in the Owned state is responsible for responding to snoop requests with the current data.

Here's the key advantage: in MESI, if Core 0 modifies a cache line (entering Modified state) and then Core 1 wants to read it, the Modified line must first be written back to main memory before Core 1 can read it. That's two operations: a write-back and a read. With MOESI's Owned state, Core 0 can transfer the data directly to Core 1 without involving main memory at all. Core 0 transitions from Modified to Owned, Core 1 enters Shared state, and main memory continues to hold stale data.

This cache-to-cache transfer eliminates a memory write-back, reducing bus traffic and latency. The trade-off is complexity: the protocol must ensure that when multiple caches hold a line in Shared state, exactly one of them (the Owned cache) responds to snoop requests, not all of them. And eventually, when the Owned line is evicted, it must be written back to memory to ensure durability.

"Modified Owned Exclusive Shared Invalid (MOESI) is a full cache coherency protocol that encompasses all of the possible states commonly used in other protocols."

- Wikipedia, MOESI Protocol

MOESI shines in producer-consumer workloads where one core writes data that many other cores then read. Scientific simulations, graphics rendering, and data analytics often exhibit this pattern. In these scenarios, MOESI reduces memory bandwidth consumption by allowing dirty data to be shared directly between caches without the penalty of write-back-then-read cycles.

AMD processors have historically favored MOESI, while Intel took a different path with MESIF.

While both Intel and AMD x86 processors maintain cache coherence, they implement subtly different protocols that reflect different architectural priorities.

Intel's MESIF protocol adds a Forward (F) state instead of Owned. Like MOESI's Owned state, Forward designates a single cache as the responder for shared data. But there's a crucial difference: Forward lines are clean, matching main memory, whereas Owned lines are dirty. When multiple caches hold a line in Shared state under MESIF, exactly one holds it in Forward state and acts as the designated responder. This reduces the thundering herd problem where every cache holding a Shared line attempts to respond to a snoop request simultaneously.

Intel designed MESIF for cache-coherent non-uniform memory architecture (NUMA) systems, where cache-to-cache transfers between sockets can be faster than accessing remote memory. The Forward state reduces redundant multicast traffic - instead of multiple caches all responding to a read request, only the Forward cache responds. Because Forward lines are clean, they can be evicted without write-back, simplifying some transitions.

AMD's MOESI, on the other hand, optimizes for scenarios where dirty data needs to be shared. In multi-socket AMD EPYC servers or Ryzen desktops with multiple chiplets, the Owned state allows modified data to propagate between cache hierarchies without round-tripping through memory. This is particularly valuable in NUMA configurations where memory access latencies vary dramatically depending on which socket owns the physical memory.

The practical differences manifest in specific workloads. Benchmarks comparing Intel and AMD systems often show performance variations in multi-threaded code that aren't explained by core count, clock speed, or IPC alone. Part of that variance stems from how the coherence protocol handles shared data patterns. Workloads with heavy producer-consumer patterns may favor MOESI, while workloads with lots of read-mostly sharing may favor MESIF.

Underneath MESI and MOESI lie two fundamentally different implementation approaches: snooping-based and directory-based coherence.

Snooping protocols rely on a shared bus or interconnect that all caches can monitor. Every cache controller snoops every transaction - reads, writes, invalidations - and updates its own state accordingly. When Core 0 writes to a Shared line, it broadcasts an invalidation message. All other cores snoop this message and, if they hold a copy, transition it to Invalid state.

Snooping works beautifully for small numbers of cores because broadcast is simple and fast. But it doesn't scale. As core counts climb into the dozens or hundreds, broadcasting every cache transaction to every cache becomes a bandwidth nightmare. The interconnect becomes saturated with snoop traffic, and performance degrades.

Directory-based protocols solve the scalability problem by maintaining a directory - essentially a table that tracks which caches hold copies of each cache line. When Core 0 wants to invalidate a line, it consults the directory to determine which caches actually hold copies and sends targeted invalidation messages only to those caches. This point-to-point communication scales far better than broadcast.

Modern processors use hybrid approaches. Within a single chip, especially for L1 and L2 caches, snooping is common because the core count is manageable. But across multiple sockets or in systems with dozens of cores, directory-based coherence takes over. AMD's Infinity Fabric and Intel's mesh interconnect both incorporate directory structures to manage coherence traffic efficiently at scale.

The directory itself can be centralized or distributed. A centralized directory lives in one place - often alongside the last-level cache or memory controller - and handles all coherence queries. A distributed directory partitions the address space, with each segment's directory co-located with the memory or cache that stores that address range. Distributed directories scale better but require more complex routing logic.

Understanding coherence protocols helps diagnose two of the most insidious performance killers in multi-threaded code: false sharing and cache line bouncing.

False sharing occurs when two independent variables, accessed by different cores, happen to reside in the same cache line. Cache coherence operates at cache-line granularity - typically 64 bytes on x86 processors. If Core 0 writes to variable A and Core 1 writes to variable B, but both variables share a cache line, the coherence protocol treats them as conflicting accesses. Each write forces the entire cache line to be invalidated and transferred between caches, even though A and B are logically independent.

On an AMD Zen4 system with 16 cores and 32 threads, concurrent access to falsely shared data required over 300 times more computing time than single-threaded access. That's two orders of magnitude lost to coherence traffic.

The performance impact is brutal. A benchmark on an AMD Zen4 system with 16 cores and 32 threads showed that concurrent access to falsely shared data required over 300 times more computing time than single-threaded access. That's two orders of magnitude lost to coherence traffic.

Mitigation strategies include padding structures to ensure frequently modified variables occupy separate cache lines, reordering structure members, or using compiler-specific alignment directives. The Linux kernel, databases, and high-performance libraries all employ these techniques extensively. But the first step is detection, which requires either careful code review or specialized profiling tools that can attribute cache misses to coherence traffic.

Cache line bouncing happens when two or more cores repeatedly write to the same cache line in quick succession. Each write forces the line into Modified state in one cache and Invalid state in others. The cache line "bounces" between cores, spending most of its time in transit rather than being useful. Locks and atomic variables are particularly susceptible because they're designed to be shared and frequently modified.

One solution is to reduce sharing by using core-local variables and aggregating results at the end of a computation. Another is to batch updates so that each core modifies a shared variable less frequently, reducing the rate of bouncing. Lock-free data structures often employ techniques like combining trees or flat combining to minimize coherence traffic.

In NUMA systems, coherence penalties compound with memory locality issues. If Core 0 on Socket 0 modifies data that Core 8 on Socket 1 is reading, the coherence protocol must coordinate across sockets, traversing inter-socket links that are slower than intra-socket communication. Proper NUMA-aware allocation - placing data physically close to the cores that use it - interacts with coherence to determine overall performance.

The rise of chiplet-based designs and heterogeneous computing is forcing coherence protocols to evolve beyond their original design constraints.

AMD's Ryzen and EPYC processors use a chiplet architecture where multiple CPU dies are connected via Infinity Fabric. Each chiplet has its own cache hierarchy, and maintaining coherence across chiplets involves higher latency and more complex directory structures than traditional monolithic dies. The coherence protocol must now handle variable hop counts - accessing data cached on the same chiplet is fast, on an adjacent chiplet slower, on a remote socket slower still.

Intel's Foveros and other 3D stacking technologies introduce vertical cache hierarchies where dies are stacked and connected through through-silicon vias (TSVs). Coherence protocols need to understand this topology to optimize snoop routing and minimize latency.

Heterogeneous systems complicate matters further. When a CPU, GPU, and specialized accelerators share the same memory space, maintaining coherence between fundamentally different cache hierarchies becomes a challenge. NVIDIA's Grace CPU-GPU architecture and AMD's Instinct MI300 series tackle this by implementing cache-coherent interconnects like NVLink-C2C that extend coherence protocols across CPU and GPU caches. But GPUs have different caching behavior - they favor throughput over latency, use larger cache lines, and have massive parallelism - so coherence traffic patterns differ radically from CPU workloads.

"The MESI protocol is an invalidate-based cache coherence protocol, and is one of the most common protocols that support write-back caches."

- Wikipedia, MESI Protocol

Another frontier is persistent memory and CXL (Compute Express Link). When memory is non-volatile, coherence must interact with durability guarantees. A cache line in Modified state represents uncommitted data; if power fails before write-back, that data is lost. Coherence protocols must expose primitives for flushing and fencing that software can use to enforce persistence orders, effectively extending the state machine to reason about volatility boundaries.

While this discussion has focused primarily on x86, other architectures implement coherence differently, reflecting different design philosophies and use cases.

ARM processors typically implement variants of MOESI for multi-core coherence, but with significant flexibility. ARM's architectural specification defines the memory model and ordering guarantees but leaves cache coherence implementation details to vendors. This allows Apple, Qualcomm, AWS, and others to optimize coherence for their specific workloads. Apple's M-series chips, for instance, have distinct cache behaviors for performance and efficiency cores, with a coherent interconnect tying them together.

RISC-V, as an open ISA, provides even more flexibility. RISC-V's memory model (RVWMO) specifies ordering rules but doesn't mandate a specific coherence protocol. Implementers can choose snooping, directory, or hybrid approaches. This freedom enables innovation - research projects and startups can experiment with novel coherence mechanisms without architectural constraints - but also creates fragmentation, as different RISC-V implementations may have wildly different coherence characteristics.

IBM's POWER architecture and its derivatives have historically used sophisticated directory-based protocols to scale to large core counts. POWER processors emphasize reliability and scalability for servers, so their coherence protocols include features like in-flight transaction tracking and aggressive prefetching that interact with coherence state.

Understanding coherence doesn't just satisfy curiosity - it directly informs how to write faster parallel code. Here are key takeaways:

1. Mind your cache lines. The 64-byte cache line is the fundamental unit of coherence. Group read-only data together, separate frequently modified data, and pad critical structures to avoid false sharing. Tools like Intel VTune and AMD uProf can identify cache line contention in running programs.

2. Reduce sharing. The fastest cache line is one that's Exclusive or Modified in a single cache. Architect your algorithms to maximize thread-local data and minimize shared state. When sharing is necessary, batch updates to reduce coherence traffic.

3. Understand memory ordering. Coherence protocols interact with memory models to provide ordering guarantees. On x86, acquire/release semantics are relatively cheap because the strong memory model aligns with coherence protocol behavior. On ARM and RISC-V, which have weaker memory models, explicit barriers may be required, and these interact with coherence.

4. Profile coherence traffic. Modern CPUs expose performance counters for cache coherence events - snoop hits, snoop misses, cache-to-cache transfers, invalidations. Learning to interpret these counters reveals whether slowdowns stem from coherence overhead or other bottlenecks.

5. Respect NUMA. On multi-socket systems, coherence latencies vary by topology. Use NUMA-aware allocation APIs, pin threads to cores near their data, and minimize cross-socket sharing.

The coherence protocol is always working, whether you think about it or not. The question is whether you'll work with it or against it.

As computing architectures continue to diversify, coherence protocols face new pressures. The end of Dennard scaling means power efficiency is paramount, yet coherence traffic consumes power and bandwidth. Research efforts explore low-power coherence mechanisms, such as selectively disabling snooping for power-insensitive data or using approximate coherence for error-tolerant applications.

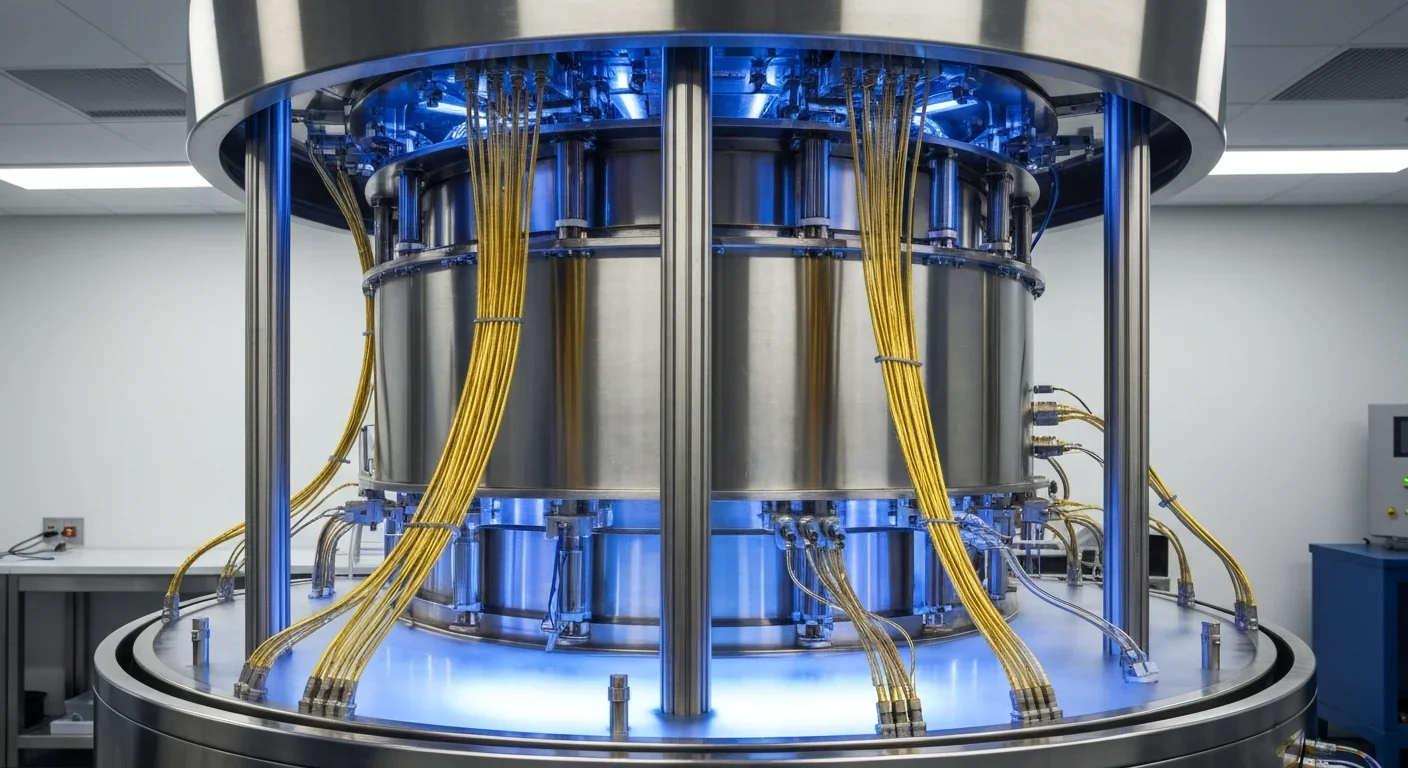

Quantum computing and neuromorphic architectures might render traditional coherence irrelevant, as their computational models differ fundamentally from von Neumann architectures. But for conventional processors, coherence remains essential.

Emerging interconnect standards like CXL promise to democratize coherence, allowing third-party accelerators and memory expanders to participate coherently in shared memory systems. This standardization could unlock new forms of composable computing, where coherent devices are mixed and matched like Lego blocks.

Meanwhile, the protocols themselves are becoming smarter. Machine learning models trained on workload traces can predict coherence traffic patterns and proactively prefetch or invalidate cache lines, reducing latency. Hardware-software co-design is exploring coherence hints, where compilers or runtimes provide the hardware with semantic information about sharing patterns, enabling more efficient protocol decisions.

Cache coherence protocols are the hidden choreography that keeps your multi-core processor functioning. They operate billions of times per second, coordinating cores with surgical precision so that your multi-threaded programs see a consistent view of memory. MESI and MOESI, with their elegant state machines and carefully optimized transitions, represent decades of hardware engineering distilled into protocols that rarely receive the recognition they deserve.

For software developers, understanding these protocols transforms abstract performance advice into concrete mental models. False sharing isn't a mysterious slowdown - it's the coherence protocol doing exactly what it must, invalidating and transferring cache lines because you placed data badly. Cache line bouncing isn't a random glitch - it's cores fighting over ownership because you architected excessive sharing.

The next time you write a parallel algorithm or debug a performance anomaly, remember: beneath your code, invisible hardware protocols are negotiating every memory access, ensuring consistency without you lifting a finger. And if you understand their rules, you can write code that dances with them instead of stumbling blindly.

Saturn's moon Titan may harbour liquid water beneath its frozen crust, kept from freezing by ammonia acting as a natural antifreeze. New Cassini data suggests the interior could be slush with warm water pockets rather than a global ocean, and NASA's Dragonfly mission launching in 2028 aims to investigate whether this exotic environment could support life.

Bacteroides thetaiotaomicron uses 88 specialized gene clusters and over 260 enzymes to decode and digest dietary fibers humans can't break down, converting them into essential short-chain fatty acids. When fiber runs out, it eats your gut's protective mucus instead, with cascading health consequences.

Scientists are restoring Ice Age ecological dynamics through rewilding projects like Siberia's Pleistocene Park and de-extinction efforts by Colossal Biosciences. These initiatives aim to reintroduce megafauna or their proxies to repair broken ecosystems, protect Arctic permafrost, and slow climate change.

The cheerleader effect is a proven cognitive bias where people look more attractive in groups because the brain automatically averages faces, smoothing out individual flaws. Research shows the sweet spot is 3-5 people, it works for all genders, and it has real implications for dating apps and social media strategy.

The Hawaiian bobtail squid farms bioluminescent bacteria in a specialized light organ to erase its shadow in moonlit waters. This partnership, where bacteria reshape the squid's body and communicate through quorum sensing, is teaching scientists how host-microbe relationships work and inspiring new medical and biotech applications.

Millions are leaving social media platforms driven by privacy scandals, mental health concerns, and algorithmic manipulation. While 60% relapse within a week, those who stay away report dramatically improved wellbeing, and decentralized alternatives like Bluesky are surging.

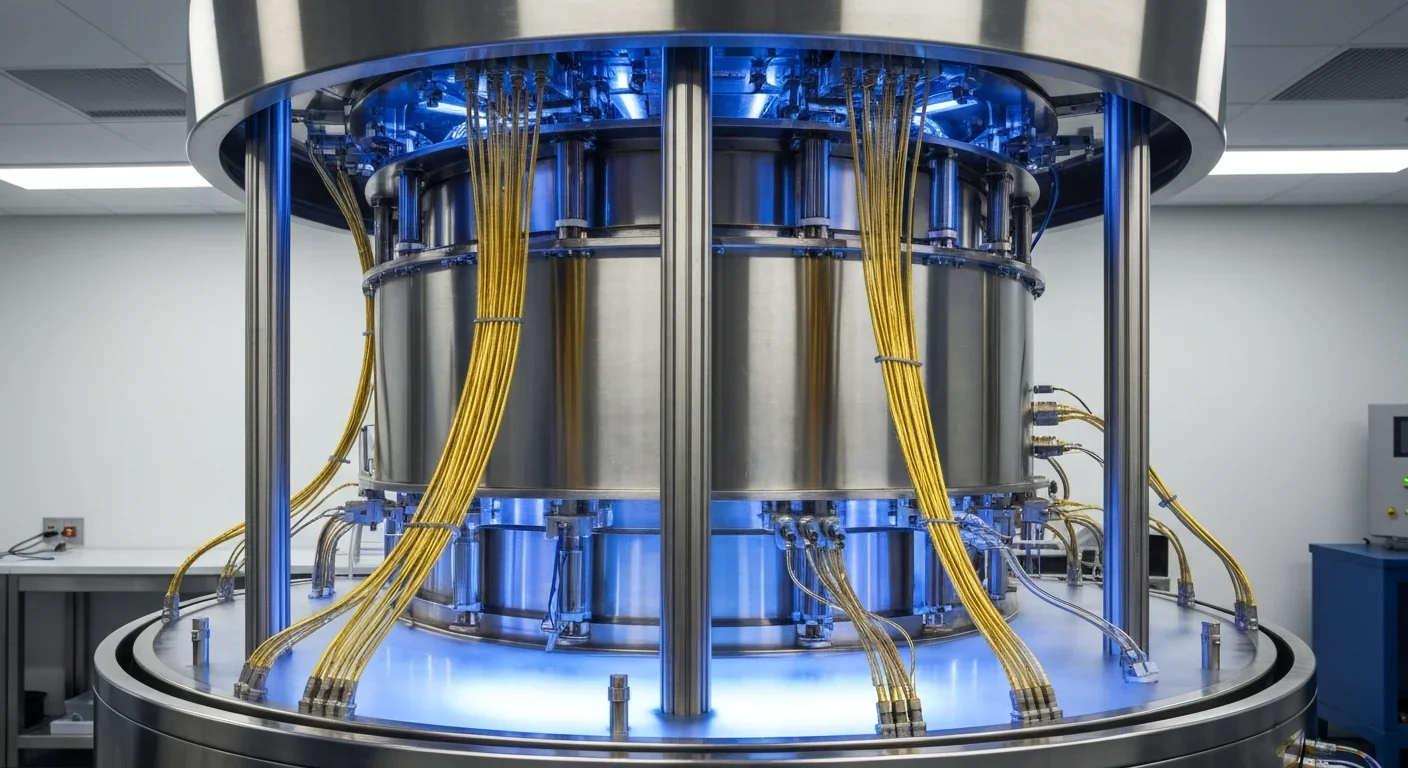

Building a reliable quantum computer requires roughly 1,000 fragile physical qubits per logical qubit due to surface code error correction overhead. New code families like LDPC and neutral-atom platforms are racing to slash that ratio, with some teams claiming it could drop to as few as 5-to-1.