Why Quantum Computers Need 1,000 Qubits for One

TL;DR: Stochastic computing, a 1960s paradigm encoding numbers as random bit streams, is making a comeback as a path to ultra-low-power AI hardware. Recent prototypes achieve 1,000x better energy efficiency than conventional chips, making edge AI in sensors and wearables finally practical.

The next technological revolution won't come from building bigger chips. It'll come from embracing randomness.

Right now, running a single neural network inference on conventional hardware can consume watts to hundreds of watts. Your smartwatch, your air quality sensor, your hearing aid, they operate on power budgets measured in milliwatts or less. That gap between what AI demands and what tiny devices can deliver isn't just an engineering inconvenience. It's the bottleneck keeping intelligent computing out of billions of everyday objects. And the solution might be a computing paradigm that most engineers forgot existed: stochastic computing, a method first sketched in the 1960s that trades precision for radical simplicity.

Here's the counterintuitive breakthrough driving a wave of new research: what if you represented numbers not as fixed binary digits, but as streams of random bits where the probability of seeing a "1" encodes the value? A stream where 70% of bits are ones represents the number 0.7. It sounds wasteful, maybe even reckless. But it unlocks something remarkable.

In conventional digital hardware, multiplying two 8-bit numbers requires a circuit with hundreds or thousands of logic gates. In stochastic computing, that same multiplication requires a single AND gate. One gate. Feed two independent bit streams into an AND gate, and the output stream's probability of being "1" equals the product of the two input probabilities. Addition becomes similarly trivial with multiplexers or simple counters. The complex multiply-accumulate operations that dominate neural network inference, the operations that make conventional AI accelerators so power-hungry, collapse into circuits so small they're almost invisible on silicon.

Recent prototype chips have demonstrated this isn't just theory. A stochastic computing-in-memory design called DS-CIM achieved an energy efficiency of 3,566 TOPS/W (tera-operations per second per watt) while running ResNet18 image classification at 94.31% accuracy. For comparison, leading conventional accelerators typically deliver tens to low hundreds of TOPS/W. And a hardware-efficient stochastic binary CNN showed roughly 1,000 times better energy efficiency than floating-point digital implementations, with memory savings of 45 times.

A stochastic multiplier needs just one AND gate. A conventional 8-bit binary multiplier needs hundreds or thousands. That simplicity is the key to thousand-fold power savings.

The story of stochastic computing begins before most of today's chip designers were born. John von Neumann explored the idea of building reliable systems from unreliable components in the 1950s, reasoning that probability-based computation could tolerate the noisy, failure-prone hardware of his era. But the first practical stochastic computing architectures emerged independently from Brian Gaines and Wolfgang Poppelbaum in the mid-1960s, built from commodity TTL integrated circuits that each contained just a handful of transistors.

Those early machines were surprisingly capable. Gaines built systems that could perform multiplication, division, and even square root operations using circuits so simple they fit on a few breadboards. One remarkable early application was a small autonomous neural network robot that used stochastic computing for radar tracking, essentially performing real-time pattern recognition decades before "deep learning" entered the vocabulary. Memory in these systems was elegantly simple: just delay lines that stored bit streams as they flowed through the circuit, no DRAM cells required.

But history wasn't kind to the approach. As Moore's Law made transistors cheap and abundant, the semiconductor industry chose a different path: pack more precise digital logic onto each chip. Binary arithmetic won because transistors became plentiful enough that the gate-count savings of stochastic computing no longer justified its accuracy trade-offs. For nearly four decades, the technique gathered dust in academic journals.

What changed? The deep learning revolution created an energy problem that conventional scaling can't solve. Training and deploying neural networks now consumes enormous amounts of electricity, and the demand is growing exponentially. The places where AI could do the most good, embedded sensors monitoring air quality, wearable health devices tracking cardiac rhythms, agricultural drones surveying crops, are precisely the places where power is scarcest. Suddenly, a paradigm that sacrifices some precision for thousand-fold reductions in power consumption looks less like a curiosity and more like a necessity.

Understanding why stochastic computing excites hardware designers requires grasping just how dramatically it simplifies neural network math.

A neural network's core operation is the multiply-accumulate, or MAC: multiply each input by a weight and sum the results. In conventional 8-bit digital hardware, each multiplication needs a dedicated multiplier circuit consuming substantial area and power. Scale that to millions of MACs per inference, and you understand why GPU-class hardware burns hundreds of watts running neural networks.

Stochastic computing flattens this hierarchy. Each multiplication is a single AND gate. Each addition is a simple counter. The entire MAC operation that would normally require a complex arithmetic unit reduces to a handful of gates. And because the circuits are so small, they can operate at near-threshold supply voltages, the point where conventional digital logic becomes unreliable but stochastic circuits keep working, since a few corrupted bits barely shift the probability. This inherent fault tolerance is what gives stochastic computing its edge for ultra-low-power operation.

There's a beautiful alignment with how neural networks actually work. Neural networks are fundamentally approximate computing systems that tolerate considerable noise in their internal representations. Stochastic computing's slight imprecision maps naturally onto this tolerance. You don't need 32-bit floating point accuracy to tell whether a photo contains a cat.

"Stochastic computing is essentially an early analog/digital hybrid that can be built with simple logic and is surprisingly robust against noise."

- Scott Locklin, science writer and quantitative researcher

Stochastic computing isn't free. Three fundamental challenges have kept researchers busy for decades.

First, accuracy. Because values are encoded as probability estimates, the precision of any computation depends on how many bits you observe. Achieving N bits of precision requires a bit stream roughly 2^N bits long, creating an exponential relationship between precision and computation time. An 8-bit-precise result needs a 256-bit stream; 16-bit precision would demand 65,536 bits. This exponential scaling puts hard limits on how precise stochastic computations can economically be.

Second, latency. Those long bit streams take time to generate and process. Where a conventional multiplier produces a result in one clock cycle, a stochastic multiplier might need 256 cycles for 8-bit precision. For real-time applications, this latency penalty can be a deal-breaker unless clever design compensates for it.

Third, correlation. The mathematical guarantee that an AND gate performs multiplication only holds when the two input bit streams are statistically independent. When intermediate results feed back into later computations, as happens throughout neural networks, correlations creep in and degrade accuracy. Managing these correlations requires careful circuit design, often involving decorrelation elements that add area overhead.

The past few years have produced innovations that significantly shrink these penalties.

On the accuracy front, researchers have developed quasi-random bit stream generators using Van der Corput low-discrepancy sequences that reduce mean-squared error by up to 98% compared to traditional random number generators. By replacing truly random streams with carefully structured sequences that still appear uncorrelated, these generators achieve higher precision with shorter bit streams, directly attacking both the accuracy and latency problems simultaneously. The TranSC design using this approach reduced hardware area by 33%, power by 72%, and energy by 64% compared to previous stochastic implementations.

Hybrid architectures represent another major advance. The DS-CIM computing-in-memory design from early 2026 combines stochastic computing with SRAM-based memory, performing MAC operations directly where data is stored. By sharing a single pseudo-random number generator across an entire memory array and using a clever data remapping technique, DS-CIM eliminates the saturation errors that previously limited OR-based accumulation. The result: 94.45% accuracy on CIFAR-10 image classification with just 0.74% error, approaching conventional digital precision.

On the device level, reconfigurable field-effect transistors (RFETs) have shown that new transistor architectures can make stochastic number generators and accumulators far more compact, achieving 31% area reduction and 28% energy reduction compared to conventional FinFET implementations. And research into probabilistic bit (p-bit) circuits has demonstrated that sample-aware retraining, where neural networks are trained knowing they'll run on stochastic hardware, can recover most of the accuracy lost to binary activations.

Quasi-random bit stream generators reduce errors by up to 98% while cutting power by 72%, turning stochastic computing's biggest weakness into a manageable engineering challenge.

Perhaps most provocatively, startup Extropic is developing thermodynamic sampling units that use probabilistic bits (pbits) natively, claiming potential energy efficiency gains of 10,000 times over GPUs for certain inference workloads. Their approach generates samples from energy-based models directly in hardware, eliminating explicit matrix multiplications entirely.

The competition to build ultra-low-power AI hardware extends well beyond stochastic computing, and different regions are placing different bets.

In the United States, Intel's Loihi neuromorphic chip and IBM's NorthPole represent the neuromorphic approach, using spiking neural networks that process information as sparse, timed electrical pulses rather than dense matrix operations. These chips enable intelligent sensing at the edge without cloud connectivity, handling gesture recognition and voice activity detection at remarkably low power. Japanese and European research groups have pushed heavily into memristive computing, where resistance-based memory devices perform computation in place, eliminating the energy-hungry data shuttling between separate processor and memory units. Researchers have even demonstrated spintronic memristors where magnetic fields modulate synaptic weights, a non-electrical approach to weight tuning that could enable flexible, wearable neuromorphic systems.

Chinese research teams have been particularly active in stochastic computing-in-memory architectures, recognizing that combining SC's simple logic with in-memory computing addresses both the compute and memory-access energy challenges simultaneously. Meanwhile, spin-transfer-torque devices developed across multiple international collaborations offer yet another path, using the inherent randomness of spintronic physics as a computational resource rather than a defect to be engineered away.

The hardware approach that ultimately wins may not be a single paradigm but a combination. Emerging OxRAM resistive memory arrays can exploit their natural resistance variability to generate stochastic binary neuron outputs without dedicated random number generator circuits, effectively turning device physics into free computation. This kind of cross-technology integration, where the stochastic computing paradigm meets emerging memory devices, suggests the future isn't about choosing between approaches but combining them intelligently.

"We have developed a new type of computing hardware, the thermodynamic sampling unit (TSU), where pbits output a voltage that randomly wanders between two states, interpreted as a 1 or a 0."

- Extropic research team

Within the next decade, you'll likely carry multiple devices running AI inference on stochastic or probabilistic hardware without ever knowing it. Your fitness tracker might use a stochastic neural network consuming microwatts to continuously analyze your heart rhythm. Environmental sensors scattered across cities could run air quality models on milliwatt budgets. Agricultural monitors could process crop health images right on the sensor, no cloud upload needed.

For engineers and computer science students, this shift means rethinking assumptions. The matched-presentation training strategy, where models are trained with the same level of stochastic noise they'll encounter during inference, is becoming an essential skill. Understanding how to design neural networks that gracefully tolerate approximate arithmetic, exploiting the natural sparsity in neural network weights for additional efficiency, will separate the hardware-aware ML practitioners from those still designing for idealized, unlimited-power scenarios.

The bigger picture is this: stochastic computing's return is really a story about the end of one computing era and the beginning of another. The brute-force approach of packing ever more precise transistors onto ever larger chips is hitting physical and economic walls. The next chapter belongs to computing paradigms that work with imprecision rather than against it, that find power in probability rather than precision. A 1960s idea, born from vacuum tubes and breadboards, is being reborn in advanced silicon, and it might just be the key to putting intelligence everywhere.

Saturn's moon Titan may harbour liquid water beneath its frozen crust, kept from freezing by ammonia acting as a natural antifreeze. New Cassini data suggests the interior could be slush with warm water pockets rather than a global ocean, and NASA's Dragonfly mission launching in 2028 aims to investigate whether this exotic environment could support life.

Bacteroides thetaiotaomicron uses 88 specialized gene clusters and over 260 enzymes to decode and digest dietary fibers humans can't break down, converting them into essential short-chain fatty acids. When fiber runs out, it eats your gut's protective mucus instead, with cascading health consequences.

Scientists are restoring Ice Age ecological dynamics through rewilding projects like Siberia's Pleistocene Park and de-extinction efforts by Colossal Biosciences. These initiatives aim to reintroduce megafauna or their proxies to repair broken ecosystems, protect Arctic permafrost, and slow climate change.

The cheerleader effect is a proven cognitive bias where people look more attractive in groups because the brain automatically averages faces, smoothing out individual flaws. Research shows the sweet spot is 3-5 people, it works for all genders, and it has real implications for dating apps and social media strategy.

The Hawaiian bobtail squid farms bioluminescent bacteria in a specialized light organ to erase its shadow in moonlit waters. This partnership, where bacteria reshape the squid's body and communicate through quorum sensing, is teaching scientists how host-microbe relationships work and inspiring new medical and biotech applications.

Millions are leaving social media platforms driven by privacy scandals, mental health concerns, and algorithmic manipulation. While 60% relapse within a week, those who stay away report dramatically improved wellbeing, and decentralized alternatives like Bluesky are surging.

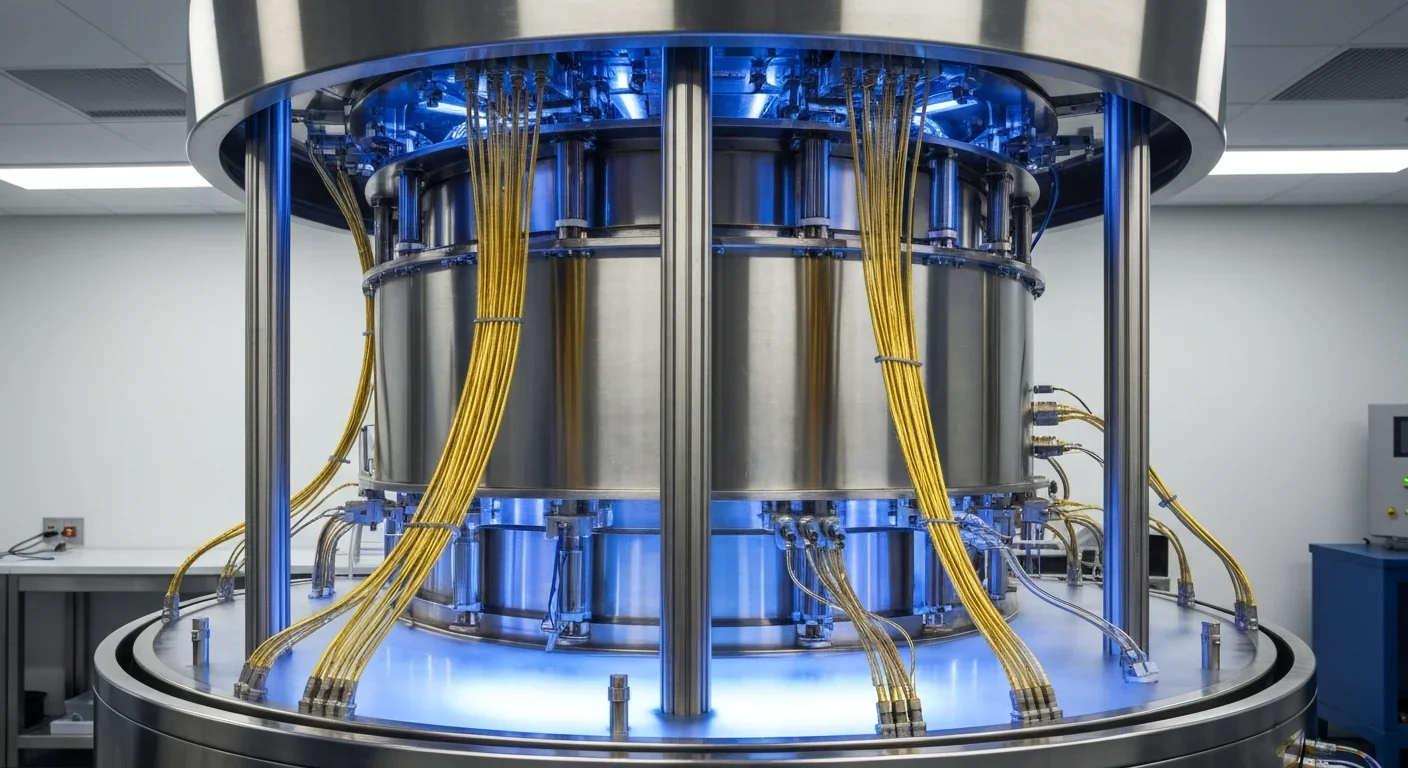

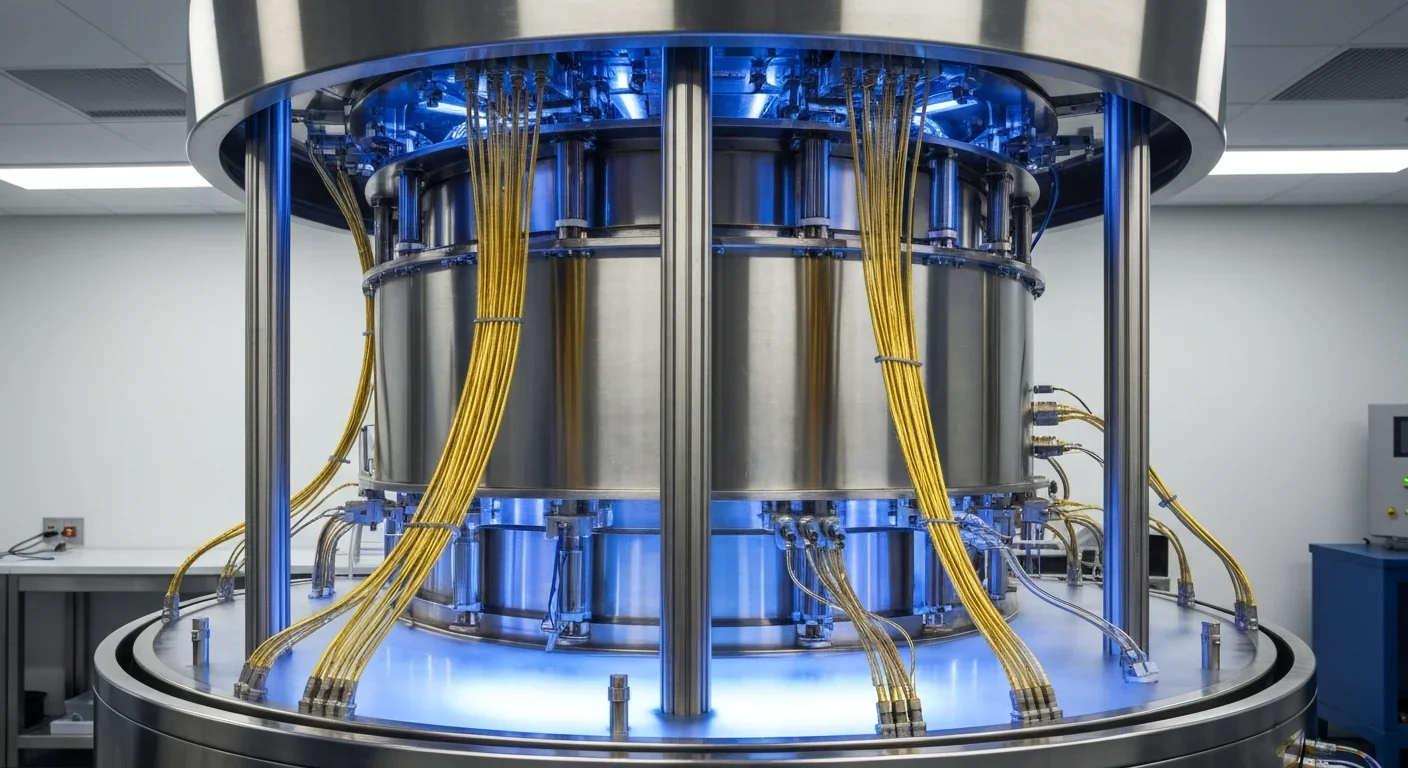

Building a reliable quantum computer requires roughly 1,000 fragile physical qubits per logical qubit due to surface code error correction overhead. New code families like LDPC and neutral-atom platforms are racing to slash that ratio, with some teams claiming it could drop to as few as 5-to-1.