Why Quantum Computing Bet on One Qubit Design

TL;DR: Processing-in-memory (PIM) architectures are eliminating the 79-year-old von Neumann bottleneck by embedding computation directly into memory chips. Major manufacturers are racing to commercialize this technology, promising doubled performance and 70% energy reduction for AI and data-intensive workloads without requiring software changes.

By 2027, computer architectures will have fundamentally changed. The von Neumann bottleneck - that 79-year-old design flaw forcing processors to wait endlessly for data - will become a relic. Processing-in-memory (PIM) technology is already here, and it's not just faster. It's restructuring how we think about computation itself.

Samsung's HBM-PIM technology, announced in 2021, delivered a staggering promise: double the system performance while slashing energy consumption by over 70%. No hardware changes. No software rewrites. Just raw architectural efficiency gained by putting computation where the data lives. Now every major memory manufacturer - Samsung, SK Hynix, Micron - is racing toward HBM4 production with embedded processing capabilities.

This isn't incremental improvement. This is the most profound shift in computer architecture since the stored-program computer emerged from World War II. And within five years, it will power everything from your phone to the data centers training AI models.

When John von Neumann designed his architecture for stored-program computers, he created an elegant solution: a single unified bus handling both data and instructions. Simple. Efficient. Revolutionary.

Also, fatally flawed.

The von Neumann architecture forces CPUs to wait. Every computation requires shuttling data back and forth between processor and memory through a shared pathway. As CPUs grew exponentially faster - executing billions of instructions per second - memory lagged behind. Modern DDR4 RAM transfers data at 25.6 GB/s. That sounds fast until you realize the processor is twiddling its circuits, massively underutilized, waiting for the next batch of data to arrive.

Computer architects have known about this bottleneck for decades. They've tried everything: cache hierarchies, separate instruction and data buses, faster memory technologies. But these are Band-Aids on a structural problem. The fundamental issue persists: computation happens in one place, data lives in another, and the gap between them keeps widening.

Processing-in-memory takes a radically different approach: don't move the data to the processor. Move the processor to the data.

The von Neumann bottleneck has persisted for 79 years not because engineers ignored it, but because solving it required a fundamental rethinking of what a computer is. PIM finally makes that leap.

The technical elegance of PIM lies in its simplicity. Traditional systems treat memory as passive storage - a warehouse of bits waiting to be fetched. PIM treats memory as an active computational substrate.

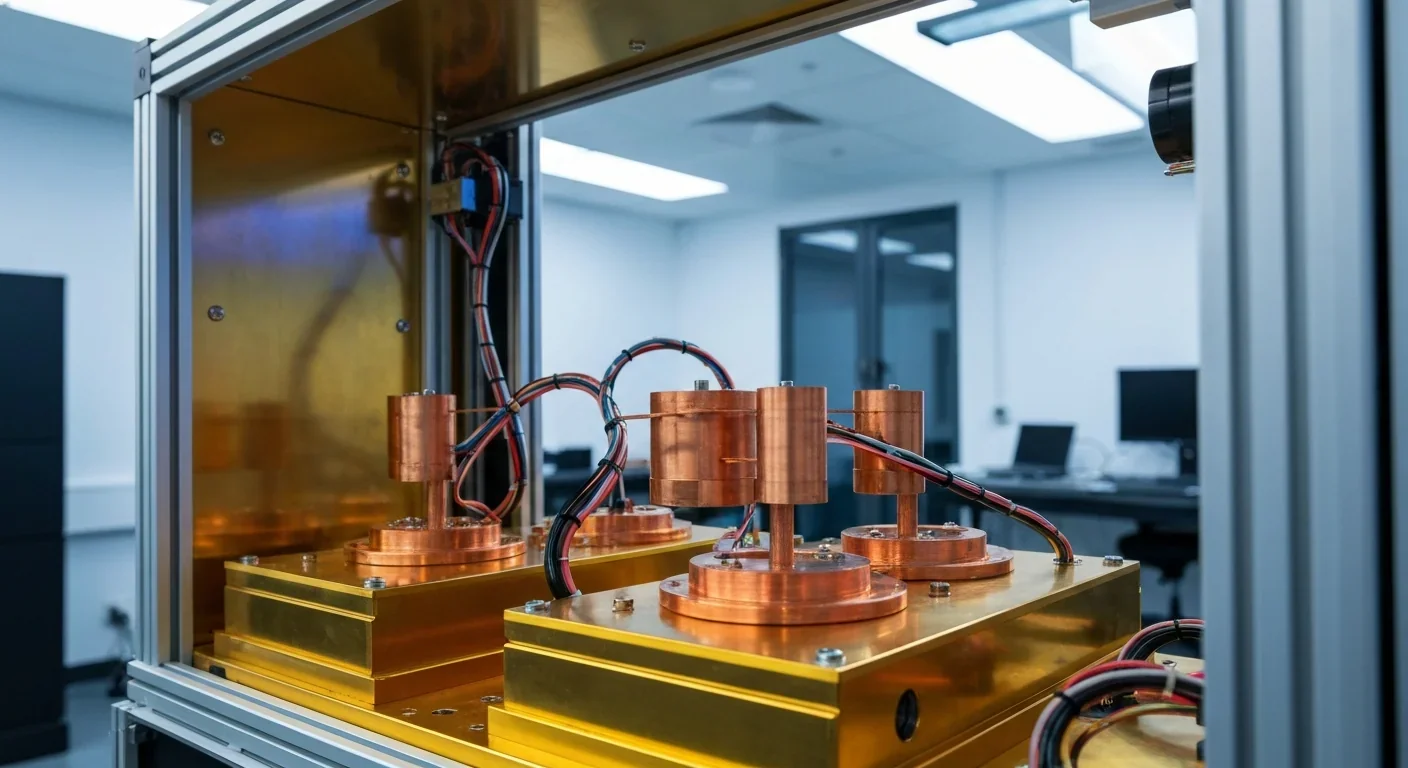

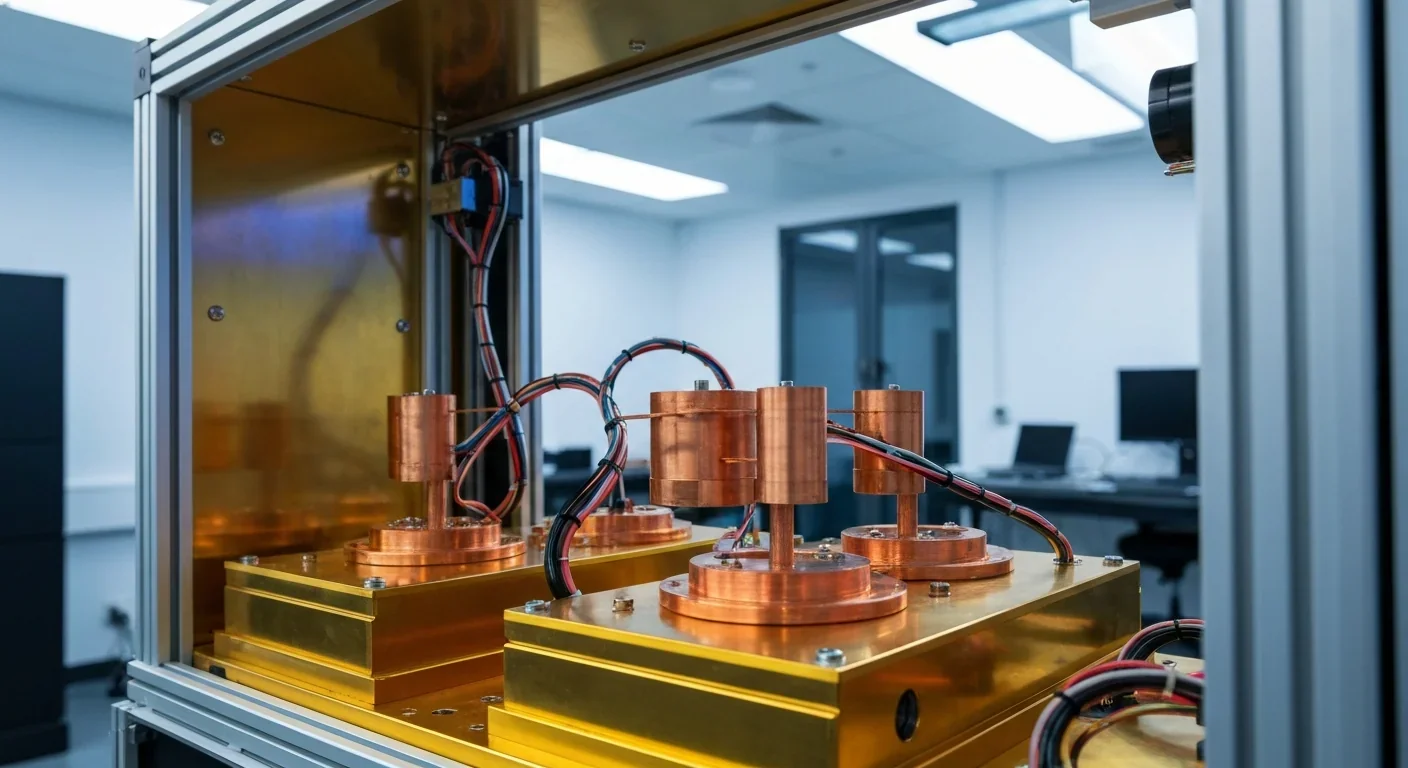

Samsung's HBM-PIM implementation places a DRAM-optimized AI engine inside each memory bank. These aren't full-fledged CPUs trying to do everything. They're specialized processors designed for specific operations that benefit most from proximity to data: matrix multiplications, database filtering, parallel searches.

The architecture enables what's called "bank-level parallelism." Instead of one processor crunching through operations sequentially, dozens of processing units work simultaneously within their respective memory banks. An AI inference operation that would require shuffling gigabytes of weights and activations between CPU and memory now happens entirely within memory itself. Inter-chip data traffic drops to near zero.

This isn't theoretical. UPMEM, a commercial PIM technology provider, already offers DRAM-PIM accelerators for database and analytics workloads. Their systems demonstrate measurable improvements in real-world applications: SQL joins, stream processing, approximate nearest neighbor search.

The breakthrough isn't just technical - it's backward compatible. You don't need to rewrite software or redesign entire systems. The PIM unit presents itself as high-bandwidth memory to the rest of the computer, handling certain operations internally while appearing transparent to the software stack.

Walk into any AI data center today and you'll find NVIDIA's latest accelerators: H200s with 141 GB of high-bandwidth memory, B200s with 192 GB. AMD's countering with Instinct MI300X matching that capacity. These chips are memory-bound. Their computational power far exceeds their ability to feed themselves data.

Memory bandwidth has become the unsung bottleneck of the AI revolution. Training a large language model isn't limited by how many floating-point operations your GPU can perform. It's limited by how fast you can get those model weights from memory to the processing units.

Enter HBM4. The next generation of high-bandwidth memory will hit 2 TB/s - 2048 GB/s - through a 2048-bit interface. That's sixteen times the bandwidth of the baseline HBM1 that seemed impressive just a few years ago. Samsung has achieved 90% logic die yield, indicating mass production is imminent. They're delivering 11 Gbps pin speeds, edging ahead of competitors.

But raw bandwidth only matters if you can use it efficiently. That's where PIM transforms the equation. When computation happens inside the memory, bandwidth becomes internal throughput rather than an external constraint.

The entire memory industry has pivoted to this vision. Micron, Samsung, SK Hynix - all three confirmed HBM4 and HBM4E production intentions. The roadmap extends to 36 GB capacity in 12-Hi stacks and potentially 64 GB in 16-Hi configurations. Each generation adds more processing capability alongside storage density.

"Memory bandwidth has become the unsung hero behind the AI revolution. The chips that win aren't just about processing power - they're about how efficiently you can feed that power with data."

- Industry analysis of next-generation AI accelerators

The first wave of PIM adoption isn't coming from consumer devices. It's happening in data centers, where the economics of computation are measured in watts and square footage.

Database Analytics: Traditional database queries involve scanning massive tables, filtering rows, joining datasets. Each operation requires loading data from storage, processing it in the CPU, and writing results back. Research on DRAM-PIM filtering shows that pushing filter operations into memory eliminates most data movement. The "Membrane" system accelerates analytics by performing bank-level filtering before data ever reaches the CPU.

SQL joins at scale - one of the most data-intensive operations in computing - become dramatically faster with PIM. The SPID-Join system handles skew-resistant joins entirely within memory modules, avoiding the CPU-memory bottleneck that traditionally makes large joins so expensive.

AI Inference: When you query ChatGPT or generate an image with DALL-E, the model isn't training - it's performing inference. The model weights are loaded, your input is processed through layers of matrix multiplications, and an output emerges. Those weights can be hundreds of gigabytes. Traditional architectures load them repeatedly from memory for each computation.

PIM keeps the weights in place and performs computations where they live. Samsung's claims of 2x performance and 70% energy reduction are particularly relevant for AI inference, where the same model weights are reused millions of times across different inputs.

IBM's analog in-memory computing takes this even further. Instead of digital processing units, they use analog circuits that exploit the physical properties of memory cells themselves to perform computations. Their research on transformer models - the architecture behind GPT and similar systems - shows energy efficiency gains that compound with model size.

Edge Computing: Not all AI happens in data centers. The AI-PiM project extends RISC-V processors with PIM functional units designed for edge inference. Your phone, your car, your smart home devices - all running local AI models that need to be power-efficient because they're on batteries.

PIM enables sophisticated AI at the edge by making computation so efficient it becomes viable on low-power devices.

Recommender Systems: Netflix suggesting shows, Amazon recommending products, TikTok's eerily accurate feed - these systems process massive datasets in real-time. The AutoRAC framework demonstrates automated PIM accelerator design specifically for recommendation workloads, where the bottleneck isn't computation but data access patterns.

PIM isn't just faster - it's economically transformative. When energy consumption drops 70% while performance doubles, the return on investment becomes impossible to ignore for data center operators spending millions on power bills.

This isn't the first time someone proposed processing-in-memory. The idea dates back decades. Intel even commercialized a version with Optane DC Persistent Memory - memory that combined storage persistence with computing capabilities.

Intel discontinued Optane in 2022.

Why did earlier attempts fail? Several reasons converge:

Manufacturing complexity: Building processing logic directly into memory required manufacturing processes that could handle both dense storage arrays and complex logic circuits. DRAM fabrication and logic fabrication use different techniques optimized for different goals. Only recently has process technology matured enough to integrate both effectively.

Market timing: PIM's benefits compound with data-intensive workloads. Twenty years ago, most computing was still CPU-bound - limited by how fast processors could execute instructions, not by memory bandwidth. AI and big data analytics created workloads where memory access patterns dominate performance, making PIM's value proposition obvious.

Ecosystem lock-in: The von Neumann architecture created decades of software, tools, and programming models built around its assumptions. Introducing PIM required either rewriting everything - unthinkable - or making PIM transparent to existing software. The latter took years of research to achieve.

Economics: Developing new memory technologies costs billions. DRAM manufacturers needed certainty that a market existed before investing in PIM production lines. The AI boom provided that certainty.

Intel's Optane failed not because the technology was wrong but because it arrived too early and targeted the wrong use cases. It tried to replace DRAM with persistent memory, a massive architectural shift. Modern PIM is more strategic: enhance existing memory with processing capability, remaining compatible with current systems.

While tech headlines obsess over AI model capabilities and chip export restrictions, a quieter competition is reshaping computing infrastructure: the race to dominate PIM manufacturing.

South Korea's Semiconductor Gambit: Samsung's aggressive HBM4 development positions South Korea at the center of this transition. Samsung and SK Hynix together control the majority of global HBM production. Adding processing capabilities to their memory gives them leverage over the entire AI hardware stack.

Samsung is pursuing NVIDIA's approval for HBM4 supply - critical since NVIDIA's data center GPUs dominate AI training. Landing that contract means Samsung's PIM architecture becomes the de facto standard for AI infrastructure worldwide.

China's Semiconductor Strategy: While Western nations focus on restricting advanced chip exports to China, memory technology creates a parallel pathway. PIM enables sophisticated computing through memory architecture rather than pure processor advancement. Watch for Chinese investment in PIM research and domestic memory manufacturing as an end-run around chip restrictions.

Europe's Opportunity: The EU has historically lagged in semiconductor manufacturing, but PIM research from institutions like ETH Zurich shows Europe retains strong academic and research capabilities. Commercializing that research could give Europe a foothold in next-generation computing.

The United States' Dilemma: American companies design the chips (NVIDIA, AMD, Intel) but don't manufacture the memory. Micron is the lone U.S.-based HBM producer. As PIM becomes critical infrastructure, this dependency creates supply chain vulnerabilities.

Geopolitics and computer architecture are converging. The countries that lead in PIM manufacturing will control the infrastructure powering AI, data analytics, and high-performance computing for the next decade.

"The semiconductor industry is experiencing a fundamental shift. It's no longer just about who makes the fastest processors - it's about who controls the memory architecture that enables those processors to function efficiently."

- Analysis of global semiconductor competition

Every architectural revolution involves trade-offs. PIM solves the memory bottleneck, but it's not a universal solution.

Programming complexity: While PIM can be transparent to software, getting maximum performance requires writing code that understands the architecture. Research on PIM programming models shows developers need new tools and frameworks. The DaPPA framework attempts to provide data-parallel programming abstractions, but these add complexity.

Not every workload benefits equally. CPU-bound computations - complex branching logic, irregular memory access patterns - see little improvement. PIM excels at data-parallel operations with predictable access patterns. That's perfect for AI and databases, less relevant for traditional business applications.

Standardization challenges: UPMEM uses one PIM architecture. Samsung's HBM-PIM uses another. Future systems might use entirely different approaches. Without standards, software written for one PIM system won't work on another. The industry needs to converge on common interfaces and programming models before PIM can become truly mainstream.

Debugging and profiling: When computation happens inside memory, traditional debugging tools become less effective. You can't easily set breakpoints or inspect state within PIM units using conventional software debuggers. New modeling and simulation frameworks are emerging, but they're still research tools, not production-ready.

Cost structure: HBM is already expensive. Adding processing logic increases cost further. The economics work for high-end data center deployments where performance and energy savings justify premium pricing. Consumer devices will adopt PIM more slowly, waiting for costs to decline through manufacturing scale.

Energy efficiency paradox: Yes, PIM reduces energy for data movement. But adding processing logic to memory increases idle power consumption. For workloads with sporadic memory access, PIM might actually increase energy usage. Research on memory system efficiency shows the benefits are workload-dependent.

PIM isn't a silver bullet. It's a specialized tool that excels at specific workloads. The art of future system design will be knowing when to use PIM and when traditional architectures remain more efficient.

Within five years, PIM will be pervasive in data centers. Within ten, it'll appear in consumer devices. What does that mean for people building or using technology?

For software engineers: Start understanding data locality and memory access patterns. Code that works efficiently on von Neumann architectures might perform poorly on PIM systems. Learn about data-parallel programming models and tools like DaPPA that abstract PIM complexity.

For system architects: Redesign systems assuming memory is computational. The traditional separation between compute and storage blurs. Think about which operations should happen in PIM versus traditional processors. Architectural trade-offs between PIM and emerging alternatives like CXL-PIM require careful analysis.

For businesses: Evaluate whether your workloads benefit from PIM. Data analytics, AI inference, large-scale databases - these see immediate gains. Traditional OLTP transactions and business logic might not. PIM for OLTP is still an active research area.

For policymakers: As PIM becomes critical infrastructure, questions of supply chain security and technological sovereignty become urgent. Which countries control PIM manufacturing? What happens if geopolitical tensions disrupt access? Investment in domestic semiconductor capabilities may need to include memory, not just processors.

For researchers: PIM opens new questions. How do we optimize compilers for heterogeneous memory systems? What programming abstractions make PIM accessible? Can we extend PIM concepts to resistive RAM or other emerging memory technologies? Neuromorphic computing combining PIM with brain-inspired algorithms could create entirely new computational paradigms.

The von Neumann architecture served us well for 79 years. It enabled the computer revolution, the internet, smartphones, cloud computing, AI. But every technology eventually hits its limits.

The physics of computation are unforgiving. Moving data consumes energy and time. As transistors shrink and data volumes explode, the bottleneck between processor and memory becomes insurmountable. You can't optimize your way out of a fundamental architectural constraint.

PIM doesn't just improve computing - it transforms our assumptions about what computers are. For eight decades, we've thought of computation as something that happens in a processor, with memory as a supporting player. PIM inverts that relationship. Memory becomes the primary computational substrate, with traditional processors handling coordination and control.

The implications cascade through the entire technology stack. Operating systems will evolve new memory management strategies. Programming languages will add constructs for expressing PIM operations. Databases will redesign storage engines around in-memory processing. AI frameworks will rewrite training and inference pipelines.

This isn't a incremental improvement. It's a fundamental reimagining of how we compute.

And it's happening now. Not in research labs or future roadmaps, but in production memory chips shipping to data centers. Samsung, SK Hynix, and Micron are committed. NVIDIA and AMD are building their next-generation accelerators around PIM-capable memory. The market is projected to grow to $60 billion by 2032.

Within a decade, explaining the von Neumann bottleneck will be like explaining why we once needed separate devices for phones and cameras. "Wait, you used to move all your data to a separate chip just to do computations? Why didn't you just compute where the data was?"

The next generation of engineers will find that absurd. They'll grow up with PIM as the default architecture, von Neumann as a historical curiosity. And they'll wonder why it took us so long to figure out something so obvious: if data movement is the problem, stop moving the data.

The future of computing is already here. It's just waiting in memory.

Solar sail spacecraft navigate the solar system by tacking on sunlight, angling reflective sheets to redirect photon pressure just as sailboats tack against the wind. Missions like IKAROS and LightSail 2 have proven the physics works, and next-generation designs could enable interstellar travel.

Metformin, a cheap diabetes drug taken by 150 million people, may slow aging by mildly stressing cells through mitochondrial complex I inhibition, triggering protective AMPK pathways. The landmark TAME trial is now testing this in humans, potentially making aging itself an FDA-treatable condition.

Scientists have identified 16 climate tipping elements that can trigger each other in cascading chain reactions. New research shows five may already be at risk at current warming, and crossing just one threshold can double the number of systems that collapse.

The cheerleader effect is a proven cognitive bias where people look more attractive in groups because the brain automatically averages faces, smoothing out individual flaws. Research shows the sweet spot is 3-5 people, it works for all genders, and it has real implications for dating apps and social media strategy.

Snowshoe hares change coat color based on day length, not snow. As climate change shortens snow seasons, white hares stand out against brown landscapes, increasing predation by 7% per week. Some populations carry a borrowed gene for staying brown, offering a potential genetic lifeline.

Care workers earn poverty-level wages despite performing essential labor worth trillions globally. Historical gendering of domestic work, flawed economic models, and systemic racism entrench this undervaluation, but evidence from Nordic countries and union organizing shows that treating care as infrastructure produces massive economic returns.

Google, IBM, and every major quantum computing company converged on the transmon qubit because it offered the best trade-off between noise immunity and manufacturability. Flux qubits survive in D-Wave's annealers, and hybrid fluxonium designs may soon challenge transmon dominance.